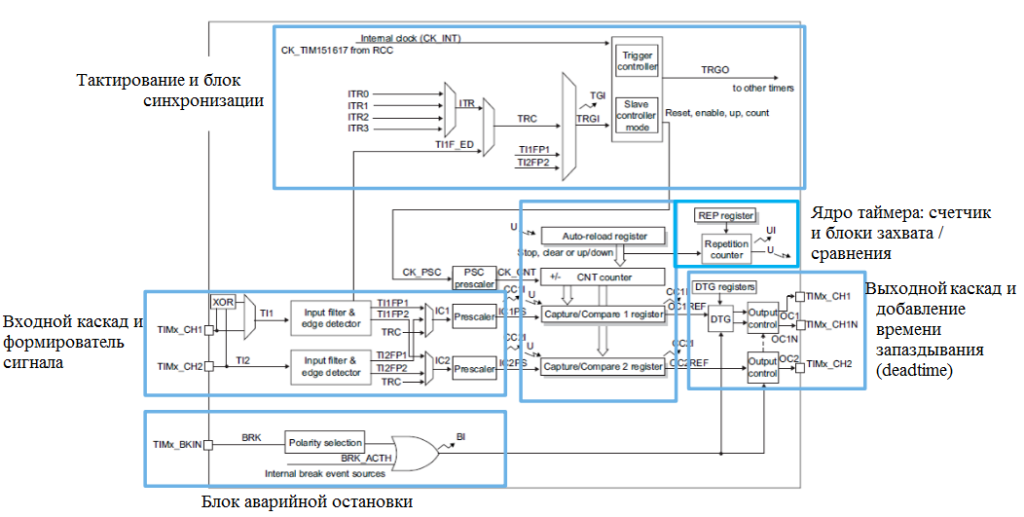

Ядро таймера состоит из 16-разрядного счетчика вверх, соединенного с регистром автоматической перезагрузки для программирования периода подсчета и счетчиком повторений для настройки частоты прерывания при переполнении счетчика. 2 канала таймера управляются двумя регистрами захвата-сравнения.

Счетчик синхронизируется от тактового генератора и контроллера запуска (Trigger controller), который также отвечает за цепочку таймера.

Слева показаны входной каскад и схема формирования входного сигнала, а справа — выходной каскад. Он включает в себя вставку времени задержки для использования комплементарных выходов ШИМ, подходящих для полумостовых силовых каскадов.

Обратите внимание, что выводы TIMxCH1 и TIMxCH2 имеются с обеих сторон, указывая на то, что они могут работать как на вход, так и на выход.

И наконец, вход TIMxBKIN может использоваться для аварийного отключения ШИМ.

Сообщить об опечатке

Текст, который будет отправлен нашим редакторам: